In diesem Artikel lernen wir die verschiedenen Arten von Flip Flops kennen, die in der digitalen Elektronik verwendet werden.

Grundlegende Flip Flops in der digitalen Elektronik

Dieser Artikel befasst sich mit den grundlegenden Flip Flop Schaltungen wie S-R Flip Flop, J-K Flip Flop, D Flip Flop und T Flip Flop zusammen mit Wahrheitstabellen und den entsprechenden Schaltsymbolen.

Bevor man sich dem Thema widmet, ist es wichtig, dass man die Grundlagen kennt. Klicken Sie auf die untenstehenden Links, um weitere Informationen zu erhalten.

Sieh dir das an: Boolesche Logik

Sieh dir das an: Logische Gatter

Sieh dir das an: Halbaddierer und Volladdierer

Flip Flops sind eigentlich eine Anwendung von logischen Gattern. Mit Hilfe der Booleschen Logik kann man mit ihnen Speicher erstellen. Flip-Flops können auch als die grundlegendste Idee eines Direktzugriffsspeichers betrachtet werden. Wenn man ihnen einen bestimmten Eingangswert vorgibt, werden sie gespeichert und ausgeführt, wenn die logischen Gatter richtig gestaltet sind. Eine breitere Anwendung von Flipflops ist hilfreich bei der Entwicklung besserer elektronischer Schaltungen.

Die am häufigsten verwendete Anwendung von Flipflops ist die Implementierung einer Rückkopplungsschaltung. Da ein Speicher auf dem Konzept der Rückkopplung beruht, können Flipflops für dessen Entwurf verwendet werden.

Es gibt hauptsächlich vier Arten von Flipflops, die in elektronischen Schaltungen verwendet werden. Sie sind

- Das einfache Flip Flop oder S-R Flip Flop

- Delay Flip Flop

- J-K Flip Flop

- T Flip Flop

S-R Flip Flop

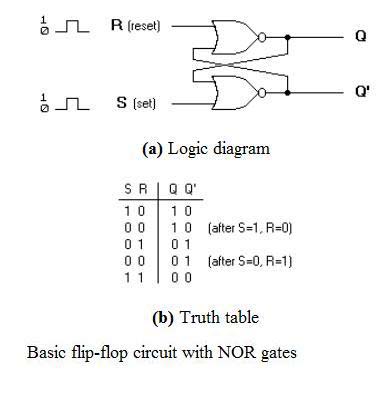

Das SET-RESET Flip Flop wird mit Hilfe von zwei NOR-Gattern und auch zwei NAND-Gattern entworfen. Diese Flip Flops werden auch S-R Latch genannt.

-

S-R Flip Flop mit NOR Gatter

Der Entwurf eines solchen Flip Flops umfasst zwei Eingänge, genannt SET und RESET . Außerdem gibt es zwei Ausgänge, Q und Q‘. Das Diagramm und die Wahrheitstabelle sind unten dargestellt.

Aus dem Diagramm ist ersichtlich, dass das Flip Flop hauptsächlich vier Zustände hat. Sie sind

S=1, R=0-Q=1, Q’=0

Dieser Zustand wird auch als SET-Zustand bezeichnet.

S=0, R=1-Q=0, Q’=1

Dieser Zustand wird als RESET-Zustand bezeichnet.

In beiden Zuständen kann man sehen, dass die Ausgänge nur Komplimente zueinander sind und dass der Wert von Q dem Wert von S folgt.

S=0, R=0-Q & Q‘ = Remember

Wenn beide Werte von S und R auf 0 geschaltet werden, dann merkt sich die Schaltung den Wert von S und R in ihrem vorherigen Zustand.

S=1, R=1-Q=0, Q’=0

Dies ist ein ungültiger Zustand, weil die Werte von Q und Q‘ beide 0 sind. Sie sollen sich gegenseitig ergänzen. Normalerweise muss dieser Zustand vermieden werden.

-

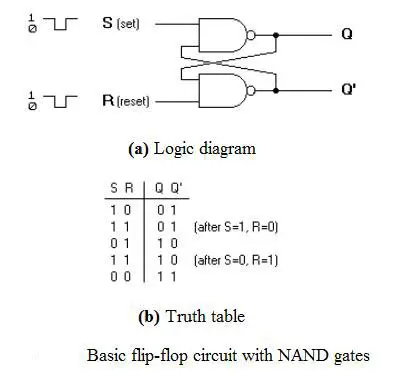

S-R Flip Flop mit NAND-Gate

Die Schaltung des S-R Flip Flops mit NAND-Gate und seine Wahrheitstabelle ist unten dargestellt.

Wie das NOR-Gate S-R Flip Flop hat auch dieses vier Zustände. Sie sind

S=1, R=0-Q=0, Q’=1

Dieser Zustand wird auch als SET-Zustand bezeichnet.

S=0, R=1-Q=1, Q’=0

Dieser Zustand wird als RESET-Zustand bezeichnet.

In beiden Zuständen kann man sehen, dass die Ausgänge nur Komplimente zueinander sind und dass der Wert von Q dem Komplimentwert von S folgt.

S=0, R=0-Q=1, & Q‘ =1

Wenn beide Werte von S und R auf 0 geschaltet werden, ist das ein ungültiger Zustand, weil die Werte von Q und Q‘ beide 1 sind. Sie sollen sich gegenseitig ergänzen. Normalerweise muss dieser Zustand vermieden werden.

S=1, R=1-Q & Q’= Remember

Wenn beide Werte von S und R auf 1 geschaltet werden, dann merkt sich die Schaltung den Wert von S und R in ihrem vorherigen Zustand.

-

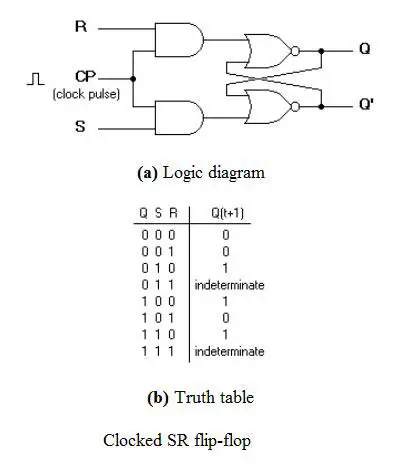

Getaktetes S-R-Flip-Flop

Es wird auch als Gated S-R-Flip-Flop bezeichnet.

Das Problem bei S-R-Flip-Flops mit NOR- und NAND-Gatter ist der ungültige Zustand. Dieses Problem kann durch die Verwendung eines bistabilen SR-Flipflops überwunden werden, das die Ausgänge ändern kann, wenn bestimmte ungültige Zustände erreicht werden, unabhängig von der Bedingung der Set- oder Reset-Eingänge. Zu diesem Zweck wird ein getaktetes S-R-Flipflop durch Hinzufügen von zwei UND-Gattern zu einem einfachen NOR-Gate-Flipflop entwickelt. Das Schaltbild und die Wahrheitstabelle sind unten dargestellt.

Ein Taktimpuls wird an die Eingänge des UND-Gatters gegeben. Wenn der Wert des Taktimpulses „0“ ist, bleiben die Ausgänge der beiden UND-Gatter „0“. Sobald ein Takt gegeben wird, wird der Wert von CP ‚1‘. Dies führt dazu, dass die Werte an S und R das NOR-Gate-Flipflop durchlaufen. Wenn jedoch die Werte von S und R auf „1“ gehen, bewirkt der HIGH-Wert von CP, dass beide für einen kurzen Moment auf „0“ gehen. Sobald der Impuls entfernt wird, nimmt das Flipflop einen Zwischenzustand ein. Es kann also einer der beiden Zustände verursacht werden, je nachdem, ob der Set- oder Reset-Eingang des Flipflops länger auf „1“ bleibt als der Übergang auf „0“ am Ende des Impulses. So können die ungültigen Zustände eliminiert werden.

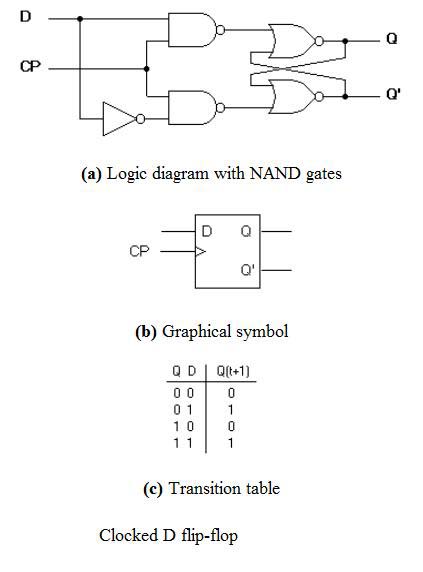

D-Flip-Flop

Das Schaltbild und die Wahrheitstabelle sind unten angegeben.

D-Flip-Flop ist eigentlich eine leichte Abwandlung des oben erläuterten getakteten SR-Flip-Flops. In der Abbildung ist zu sehen, dass der D-Eingang mit dem S-Eingang und das Komplement des D-Eingangs mit dem R-Eingang verbunden ist. Der D-Eingang wird an das Flipflop weitergeleitet, wenn der Wert von CP „1“ ist. Wenn CP HIGH ist, geht das Flip-Flop in den SET-Zustand über. Wenn er ‚0‘ ist, wechselt das Flipflop in den CLEAR-Zustand.

Um mehr über die Auslösung des Flipflops zu erfahren, klicken Sie auf den unten stehenden Link.

Sieh dir die Auslösung von Flip Flops an

Sieh dir die MASTER-SLAVE FLIP FLOP SCHALTUNG an

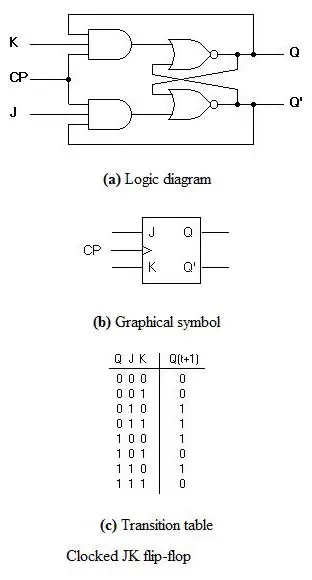

J-K Flip Flop

Der Schaltplan und die Wahrheitstabelle eines J-K Flip Flops ist unten dargestellt.

Ein J-K Flip Flop kann auch als eine Modifikation des S-R Flip Flops definiert werden. Der einzige Unterschied besteht darin, dass der Zwischenzustand raffinierter und präziser ist als bei einem S-R-Flipflop.

Das Verhalten der Eingänge J und K ist dasselbe wie das der Eingänge S und R des S-R-Flipflops. Der Buchstabe J steht für SET und der Buchstabe K steht für CLEAR.

Wenn beide Eingänge J und K den Zustand HIGH haben, schaltet das Flipflop in den Komplementärzustand. Bei einem Wert von Q = 1 schaltet es also auf Q=0 und bei einem Wert von Q = 0 schaltet es auf Q=1.

Die Schaltung enthält zwei UND-Gatter mit 3 Eingängen. Der Ausgang Q des Flipflops wird als Rückkopplung an den Eingang des UND-Gatters zurückgeführt, zusammen mit anderen Eingängen wie K und Takt. Wenn also der Wert von CP ‚1‘ ist, erhält das Flipflop ein CLEAR-Signal, unter der Bedingung, dass der Wert von Q zuvor 1 war. In ähnlicher Weise wird der Ausgang Q‘ des Flipflops zusammen mit anderen Eingängen wie J und dem Takt als Rückkopplung an den Eingang des AND gegeben. Der Ausgang wird also nur dann SET, wenn der Wert von CP 1 ist, wenn der Wert von Q‘ zuvor 1 war.

Der Ausgang kann aufgrund der Rückkopplungsverbindung im JK-Flipflop in Übergängen wiederholt werden, sobald sie für J=K=1 komplimentiert worden sind. Dies kann vermieden werden, indem man eine Zeitdauer einstellt, die kleiner ist als die Ausbreitungsverzögerung durch das Flipflop. Die Einschränkung der Impulsbreite kann mit einer Master-Slave- oder flankengesteuerten Konstruktion beseitigt werden.

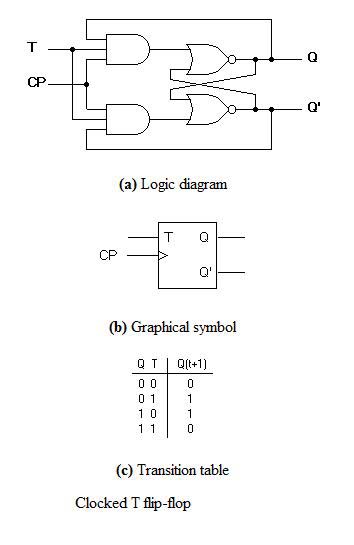

T-Flipflop

Dies ist eine viel einfachere Version des J-K-Flipflops. Die beiden Eingänge J und K sind miteinander verbunden und werden daher auch als J-K-Flipflop mit einem Eingang bezeichnet. Wenn ein Taktimpuls an das Flipflop gegeben wird, beginnt der Ausgang zu schalten. Auch hier kann die Beschränkung der Impulsbreite durch eine Master-Slave- oder flankengetriggerte Konstruktion aufgehoben werden. Schauen Sie sich die folgende Schaltung und Wahrheitstabelle an.