En este artículo, vamos a aprender sobre los diferentes tipos de flip flops utilizados en la electrónica digital.

Basic Flip Flops in Digital Electronics

Este artículo trata de los circuitos básicos de flip flop como S-R Flip Flop, J-K Flip Flop, D Flip Flop, y T Flip Flop junto con las tablas de verdad y sus correspondientes símbolos del circuito.

Antes de pasar al tema es importante que tengas conocimiento de sus fundamentos. Haga clic en los siguientes enlaces para obtener más información.

MIRA : LÓGICA BOOLEANA

MIRA : PUERTAS LÓGICAS

MIRA : MEDIA VELOCIDAD Y VELOCIDAD COMPLETA

Los flip flops son en realidad una aplicación de las puertas lógicas. Con la ayuda de la lógica booleana se puede crear memoria con ellos. Los flip flops también pueden ser considerados como la idea más básica de una Memoria de Acceso Aleatorio . Cuando se les da un determinado valor de entrada, se recuerdan y se ejecutan, si las puertas lógicas están diseñadas correctamente. Una mayor aplicación de los flip flops es útil en el diseño de mejores circuitos electrónicos.

La aplicación más utilizada de los flip flops es en la implementación de un circuito de retroalimentación. Como una memoria se basa en el concepto de retroalimentación, los flip flops se pueden utilizar para diseñarla.

Hay principalmente cuatro tipos de flip flops que se utilizan en los circuitos electrónicos. Son

- El Flip Flop básico o S-R Flip Flop

- Delay Flip Flop

- J-K Flip Flop

- T Flip Flop

S-R Flip Flop

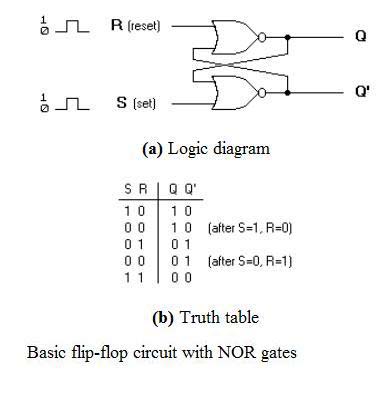

El flip flop SET-RESET está diseñado con la ayuda de dos puertas NOR y también dos puertas NAND. Estos flip flops también se llaman S-R Latch.

-

S-R Flip Flop using NOR Gate

El diseño de tal flip flop incluye dos entradas, llamadas SET y RESET . También hay dos salidas, Q y Q’. El diagrama y la tabla de verdad se muestran a continuación.

Del diagrama se desprende que el flip flop tiene principalmente cuatro estados. Son

S=1, R=0-Q=1, Q’=0

Este estado también se conoce como estado SET.

S=0, R=1-Q=0, Q’=1

Este estado se conoce como estado RESET.

En ambos estados se puede ver que las salidas son simplemente complementarias entre sí y que el valor de Q sigue al valor de S.

S=0, R=0-Q & Q’ = Recuerda

Si los valores de S y R se cambian a 0, entonces el circuito recuerda el valor de S y R en su estado anterior.

S=1, R=1-Q=0, Q’=0

Este es un estado inválido porque los valores de Q y Q’ son 0. Se supone que son complementarios entre sí. Normalmente, este estado debe ser evitado.

-

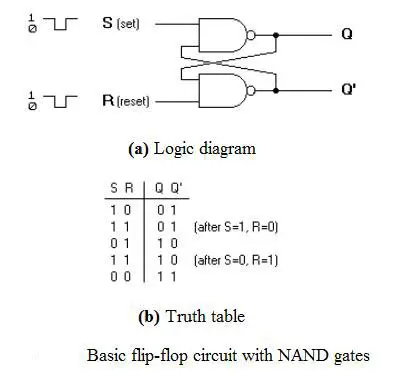

Bloqueador S-R usando Puerta NAND

A continuación se muestra el circuito del bloqueador S-R usando Puerta NAND y su tabla de verdad.

Al igual que el bloqueador S-R con Puerta NOR, éste también tiene cuatro estados. Son

S=1, R=0-Q=0, Q’=1

Este estado también se llama estado SET.

S=0, R=1-Q=1, Q’=0

Este estado se conoce como estado RESET.

En ambos estados se puede ver que las salidas son sólo complementos entre sí y que el valor de Q sigue el valor de complemento de S.

S=0, R=0-Q=1, & Q’ =1

Si ambos valores de S y R se cambian a 0 es un estado inválido porque los valores de ambos Q y Q’ son 1. Se supone que son complementos entre sí. Se supone que son complementarios entre sí. Normalmente, este estado debe ser evitado.

S=1, R=1-Q & Q’= Recuerda

Si ambos valores de S y R se conmutan a 1, entonces el circuito recuerda el valor de S y R en su estado anterior.

-

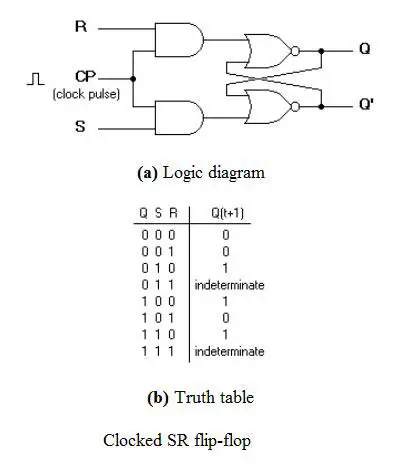

Flip flop S-R con reloj

También se denomina flip flop S-R con compuerta.

El problema de los flip flops S-R que utilizan la puerta NOR y NAND es el estado no válido. Este problema se puede superar utilizando un flip-flop SR biestable que puede cambiar las salidas cuando se cumplen ciertos estados no válidos, independientemente de la condición de las entradas Set o Reset. Para ello, se diseña un flip-flop S-R con reloj añadiendo dos puertas AND a un flip-flop básico con puerta NOR. El diagrama del circuito y la tabla de verdad se muestran a continuación.

Se da un pulso de reloj a las entradas de la compuerta AND. Cuando el valor del pulso de reloj es ‘0’, las salidas de ambas compuertas AND permanecen ‘0’. Tan pronto como se da un pulso el valor de CP se convierte en ‘1’. Esto hace que los valores de S y R pasen a través del flip flop NOR Gate. Pero cuando los valores de S y R se vuelven ‘1’, el valor HIGH de CP hace que ambos se vuelvan ‘0’ por un breve momento. En cuanto se retira el impulso, el estado del flip flop pasa a ser intermedio. Por lo tanto, cualquiera de los dos estados puede ser causado, y depende de si la entrada de set o de reset del flip-flop permanece un ‘1’ más tiempo que la transición a ‘0’ al final del pulso. Por lo tanto, los estados inválidos pueden ser eliminados.

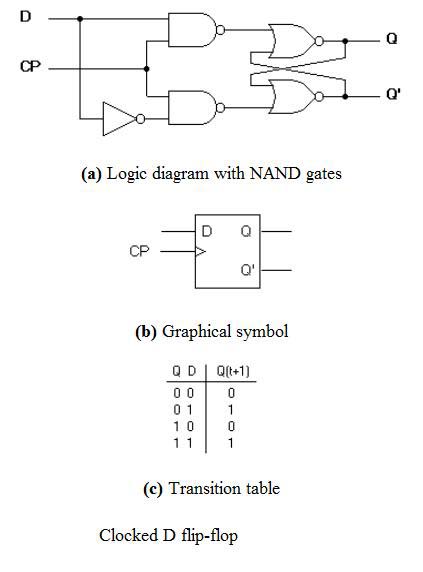

Flip Flop D

El diagrama del circuito y la tabla de verdad se dan a continuación.

El flip-flop D es en realidad una ligera modificación del flip-flop SR con reloj explicado anteriormente. En la figura se puede ver que la entrada D está conectada a la entrada S y el complemento de la entrada D está conectado a la entrada R. La entrada D pasa al flip flop cuando el valor de CP es ‘1’. Cuando CP es HIGH, el flip flop pasa al estado SET. Si es ‘0’, el flip flop pasa al estado CLEAR.

Para saber más sobre el disparo del flip flop haz clic en el siguiente enlace.

MIRA : DISPARO DE FLIP FLOPS

MIRA : CIRCUITO DE FLIP FLOP MASTER-SLAVE

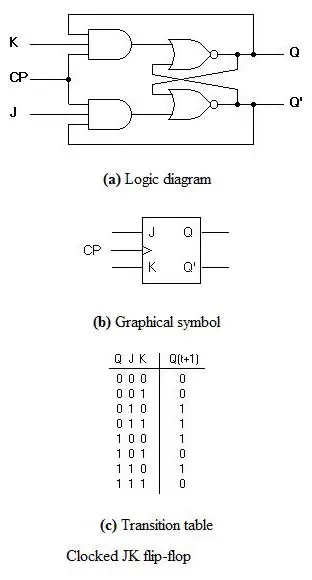

Flip FLOP J-K

A continuación se muestra el diagrama del circuito y la tabla de verdad de un flip flop J-K.

Un flip flop J-K también puede definirse como una modificación del flip flop S-R. La única diferencia es que el estado intermedio es más refinado y preciso que el de un flip flop S-R.

El comportamiento de las entradas J y K es igual al de las entradas S y R del flip flop S-R. La letra J significa SET y la letra K significa CLEAR.

Cuando ambas entradas J y K tienen un estado HIGH, el flip-flop pasa al estado de complemento. Así, para un valor de Q = 1, pasa a Q=0 y para un valor de Q = 0, pasa a Q=1.

El circuito incluye dos puertas AND de 3 entradas. La salida Q del flip flop se devuelve como retroalimentación a la entrada del AND junto con otras entradas como K y el pulso de reloj . Así, si el valor de CP es ‘1’, el flip flop recibe una señal de CLEAR y con la condición de que el valor de Q era antes 1. Del mismo modo, la salida Q’ del flip flop se retroalimenta a la entrada del AND junto con otras entradas como J y el pulso del reloj. Así que la salida se convierte en SET cuando el valor de CP es 1 sólo si el valor de Q’ era antes 1.

La salida puede repetirse en transiciones una vez que se han complementado para J=K=1 debido a la conexión de retroalimentación en el flip-flop JK. Esto puede evitarse estableciendo un tiempo de duración menor que el retardo de propagación a través del flip-flop. La restricción en la anchura del pulso puede eliminarse con una construcción maestro-esclavo o activada por flancos.

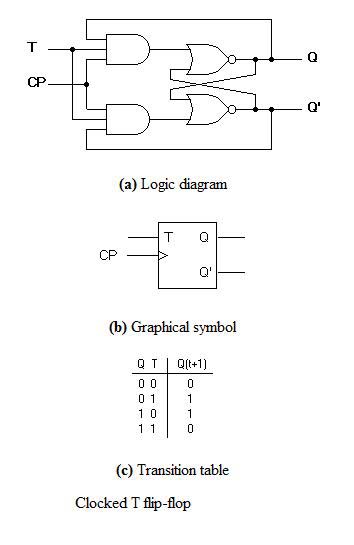

Flip Flop T

Esta es una versión mucho más simple del flip-flop J-K. Tanto la entrada J como la K están conectadas juntas, por lo que también se denomina flip flop J-K de una sola entrada. Cuando se da un pulso de reloj al flip flop, la salida comienza a alternar. Aquí también se puede eliminar la restricción de la anchura del pulso con una construcción maestro-esclavo o activada por flancos. Observe el circuito y la tabla de verdad de abajo.