V tomto článku se seznámíme s různými typy flip flopů používaných v digitální elektronice.

Základní klopné obvody v digitální elektronice

Tento článek se zabývá základními klopnými obvody, jako jsou S-R klopný obvod, J-K klopný obvod, D klopný obvod a T klopný obvod spolu s pravdivostními tabulkami a jim odpovídajícími symboly obvodů.

Než se pustíte do tématu, je důležité, abyste získali znalosti o jeho základech. Pro více informací klikněte na níže uvedené odkazy.

PODÍVEJTE SE : BOOLEAN LOGIC

PODÍVEJTE SE : LOGIC GATES

PODÍVEJTE SE : HALF ADDER AND FULL ADDER

Flip flopy jsou vlastně aplikací logických hradel. Pomocí booleovské logiky s nimi můžete vytvořit paměť. Flip flopy lze také považovat za nejzákladnější myšlenku paměti s náhodným přístupem . Když je jim zadána určitá vstupní hodnota, zapamatují si ji a provedou, pokud jsou logická hradla navržena správně. Vyšší uplatnění flip flopů je užitečné při návrhu lepších elektronických obvodů.

Nejčastěji používanou aplikací flip flopů je realizace zpětnovazebního obvodu. Protože paměť je založena na konceptu zpětné vazby, lze při jejím návrhu použít flip flopy.

Existují především čtyři typy flip flopů, které se používají v elektronických obvodech. Jsou to

- Základní klopný obvod neboli S-R klopný obvod

- Zpožďovací klopný obvod

- J-K klopný obvod

- T klopný obvod

S-R klopný obvod

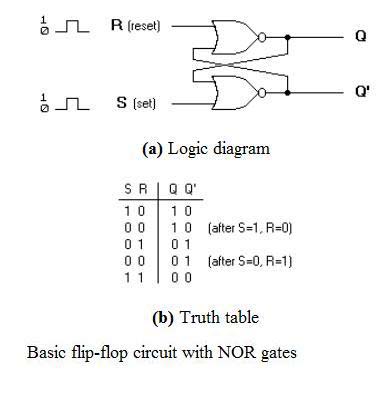

Klopný obvod SET-RESET se navrhuje pomocí dvou hradel NOR a také dvou hradel NAND. Tyto klopné obvody se také nazývají S-R Latch.

-

S-R klopný obvod pomocí hradla NOR

Konstrukce takového klopného obvodu zahrnuje dva vstupy, které se nazývají SET a RESET . Dále jsou zde dva výstupy, Q a Q‘. Schéma a pravdivostní tabulka jsou uvedeny níže.

Z diagramu je patrné, že flip flop má především čtyři stavy. Jsou to

S=1, R=0-Q=1, Q’=0

Tento stav se také nazývá stav SET.

S=0, R=1-Q=0, Q’=1

Tento stav je známý jako stav RESET.

V obou stavech je vidět, že výstupy jsou navzájem jen komplementy a že hodnota Q následuje hodnotu S.

V obou stavech je vidět, že výstupy se navzájem doplňují.

S=0, R=0-Q & Q‘ = Remember

Pokud jsou obě hodnoty S a R přepnuty na 0, pak si obvod pamatuje hodnotu S a R v předchozím stavu.

S=1, R=1-Q=0, Q’=0

Tento stav je neplatný, protože hodnoty Q i Q‘ jsou 0. Mají se navzájem doplňovat. Normálně se tomuto stavu musíme vyhnout.

-

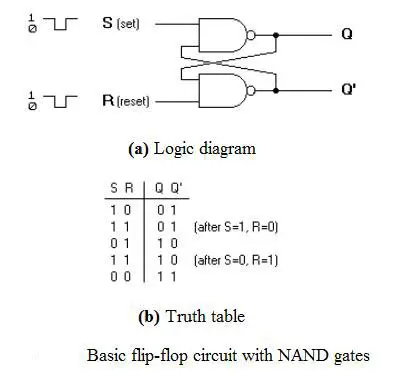

S-R klopný obvod pomocí hradla NAND

Obvod S-R klopného obvodu pomocí hradla NAND a jeho pravdivostní tabulka jsou uvedeny níže.

Stejně jako S-R klopný obvod s hradlem NOR má i tento čtyři stavy. Jsou to

S=1, R=0-Q=0, Q’=1

Tento stav se také nazývá stav SET.

S=0, R=1-Q=1, Q’=0

Tento stav je známý jako stav RESET.

V obou stavech je vidět, že výstupy se navzájem jen doplňují a že hodnota Q následuje po doplňkové hodnotě S.

S=0, R=0-Q=1, & Q‘ =1

Pokud jsou obě hodnoty S a R přepnuty na 0, jedná se o neplatný stav, protože hodnoty Q i Q‘ jsou 1.

Pokud jsou obě hodnoty S a R přepnuty na 0, jedná se o neplatný stav. Mají být navzájem komplementární. Normálně se tomuto stavu musíme vyhnout.

S=1, R=1-Q & Q’= Remember

Jsou-li obě hodnoty S a R přepnuty na 1, pak si obvod pamatuje hodnoty S a R v jejich předchozím stavu.

-

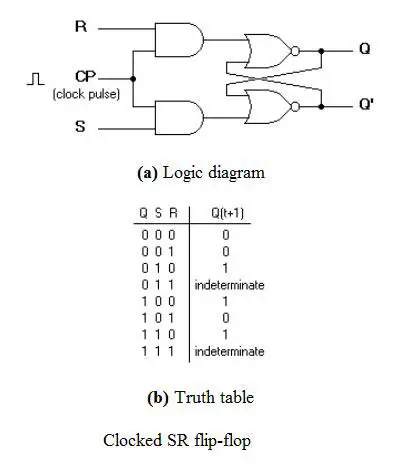

Taktovaný S-R klopný obvod

Nazývá se také Gated S-R flip flop.

Problémem S-R klopných obvodů využívajících hradla NOR a NAND je neplatný stav. Tento problém lze překonat použitím bistabilního SR flip-flopu, který může měnit výstupy při splnění určitých neplatných stavů bez ohledu na stav vstupů Set nebo Reset. Za tímto účelem je navržen taktovaný S-R flip flop přidáním dvou hradel AND k základnímu flip flopu s hradlem NOR. Schéma zapojení a pravdivostní tabulka jsou uvedeny níže.

Na vstupy hradla AND je přiveden hodinový impuls. Když je hodnota hodinového impulsu ‚0‘, výstupy obou hradel AND zůstávají ‚0‘. Jakmile je dán hodinový impulz, změní se hodnota CP na ‚1‘. To způsobí, že hodnoty na S a R projdou přes klopné hradlo NOR. Když se však hodnoty S a R změní na ‚1‘, HIGH hodnota CP způsobí, že se obě hodnoty na krátký okamžik změní na ‚0‘. Jakmile je impuls odstraněn, stav klopného obvodu se stane mezistavem. Může tedy dojít ke kterémukoli z obou stavů a záleží na tom, zda set nebo reset vstup klopného obvodu zůstane na ‚1‘ déle než přechod na ‚0‘ na konci impulsu. Neplatné stavy lze tedy eliminovat.

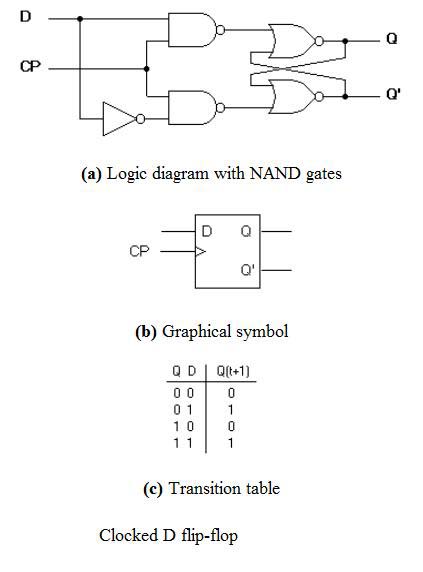

D Flip Flop

Obvodové schéma a pravdivostní tabulka jsou uvedeny níže.

D flip flop je vlastně mírnou modifikací výše vysvětleného taktovaného SR flip-flopu. Z obrázku je patrné, že vstup D je připojen ke vstupu S a doplněk vstupu D je připojen ke vstupu R. Vstup D je předán flip flopu, když je hodnota CP ‚1‘. Když je hodnota CP HIGH, přejde klopný obvod do stavu SET. Je-li hodnota ‚0‘, přejde flip flop do stavu CLEAR.

Chcete-li se dozvědět více o spouštění flip flopu, klikněte na níže uvedený odkaz.

PODÍVEJTE SE: TRIGGERING OF FLIP FLOPS

PODÍVEJTE SE: MASTER-SLAVE FLIP FLOP CIRCUIT

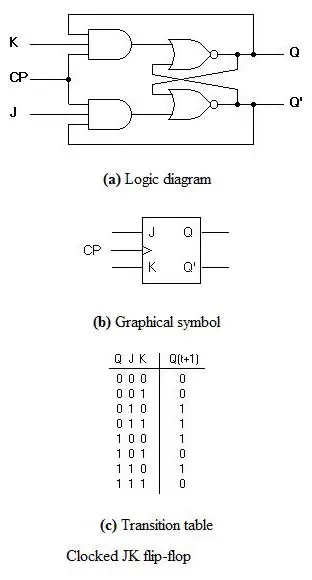

J-K Flip Flop

Níže je uvedeno schéma zapojení a pravdivostní tabulka J-K flip flopu.

J-K klopný obvod lze také definovat jako modifikaci S-R klopného obvodu. Jediný rozdíl spočívá v tom, že mezistav je jemnější a přesnější než u klopného obvodu S-R.

Chování vstupů J a K je stejné jako u vstupů S a R klopného obvodu S-R. Písmeno J znamená SET a písmeno K znamená CLEAR.

Když mají oba vstupy J a K stav HIGH, přejde klopný obvod do doplňkového stavu. Takže pro hodnotu Q = 1 se přepne do stavu Q=0 a pro hodnotu Q = 0 se přepne do stavu Q=1.

Obvod obsahuje dvě třívstupová hradla AND. Výstup Q klopného obvodu se vrací zpět jako zpětná vazba na vstup AND spolu s dalšími vstupy, jako je K a hodinový impuls . Pokud je tedy hodnota CP ‚1‘, dostane klopný obvod signál CLEAR a s podmínkou, že hodnota Q byla dříve 1. Podobně se výstup Q‘ klopného obvodu dostane jako zpětná vazba na vstup AND spolu s dalšími vstupy, jako je J a hodinový impuls. Takže výstup se stane SET, když hodnota CP je 1, pouze pokud hodnota Q‘ byla dříve 1.

Výstup se může opakovat v přechodech, jakmile byly doplněny pro J=K=1, protože ve flip-flopu JK je zpětnovazební spojení. Tomu lze zabránit nastavením doby trvání menší, než je zpoždění šíření přes klopný obvod. Omezení délky impulsu lze odstranit konstrukcí master-slave nebo konstrukcí se spouštěním po hranách.

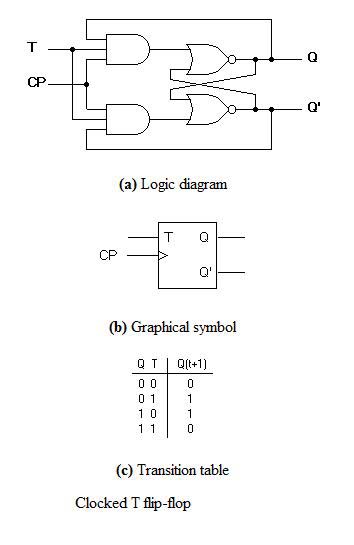

T Flip Flop

Jedná se o mnohem jednodušší verzi J-K flip flopu. Oba vstupy J a K jsou spojeny dohromady, a proto se také nazývají jednovstupový J-K flip flop. Když je do klopného obvodu přiveden hodinový impuls, výstup se začne přepínat. I zde lze omezení na šířku impulsu odstranit pomocí konstrukce master-slave nebo edge-triggered. Podívejte se na následující zapojení a pravdivostní tabulku.

.