W tym artykule, dowiedzmy się o różnych typach klapek używanych w elektronice cyfrowej.

Podstawowe układy klapek w elektronice cyfrowej

Ten artykuł dotyczy podstawowych układów klapek takich jak S-R klapka, J-K klapka, D klapka i T klapka wraz z tablicami prawdy i odpowiadającymi im symbolami układów.

Przed przejściem do tematu ważne jest abyś poznał jego podstawy. Kliknij na poniższe linki, aby uzyskać więcej informacji.

TAKE A LOOK : BOOLEAN LOGIC

TAKE A LOOK : LOGIC GATES

TAKE A LOOK : HALF ADDER AND FULL ADDER

Flip flopy są właściwie zastosowaniem bramek logicznych. Z pomocą logiki booleańskiej można za ich pomocą tworzyć pamięci. Klapki mogą być również uważane za najbardziej podstawową ideę pamięci o dostępie swobodnym. Kiedy pewna wartość wejściowa jest podana do nich, zostaną one zapamiętane i wykonane, jeśli bramki logiczne są zaprojektowane poprawnie. Wyższe zastosowanie klapek jest pomocne w projektowaniu lepszych obwodów elektronicznych.

Najczęściej stosowane zastosowanie klapek jest w realizacji obwodu sprzężenia zwrotnego. Ponieważ pamięć opiera się na koncepcji sprzężenia zwrotnego, klapki mogą być użyte do jej zaprojektowania.

Są głównie cztery typy klapek, które są używane w obwodach elektronicznych. Są to

- Podstawowy Flip Flop lub S-R Flip Flop

- Delay Flip Flop

- J-K Flip Flop

- T Flip Flop

S-R Flip Flop

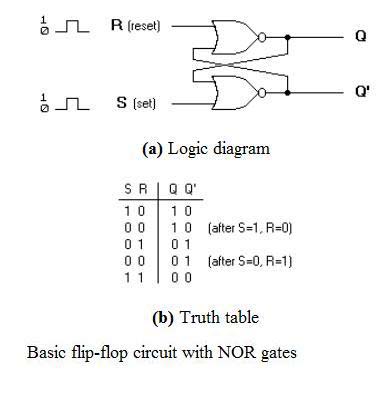

Flip Flop SET-RESET jest zaprojektowany z pomocą dwóch bramek NOR i również dwóch bramek NAND. Klapki te są również nazywane S-R Latch.

-

S-R Flip Flop using NOR Gate

Projekt takiej klapki zawiera dwa wejścia, zwane SET i RESET . Są też dwa wyjścia, Q i Q’. Schemat i tabelę prawdy przedstawiono poniżej.

Z diagramu wynika, że klapka ma głównie cztery stany. Są to

S=1, R==0-Q=1, Q’=0

Stan ten nazywany jest również stanem SET.

S=0, R=1-Q=0, Q’=1

Stan ten nazywany jest stanem RESET.

W obu stanach można zauważyć, że wyjścia są tylko komplementarne względem siebie i że wartość Q podąża za wartością S.

S=0, R=0-Q & Q’ = Remember

Jeśli obie wartości S i R są przełączone na 0, to obwód pamięta wartość S i R w poprzednim stanie.

S=1, R=1-Q=0, Q’=0

To jest stan nieprawidłowy, ponieważ wartości zarówno Q jak i Q’ są 0. Powinny one być komplementarne względem siebie. Normalnie należy unikać tego stanu.

-

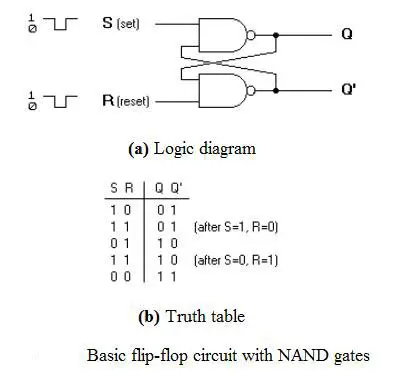

S-R Flip Flop using NAND Gate

Obwód klapki S-R wykorzystujący bramkę NAND i jej tabelę prawdy pokazano poniżej.

Podobnie jak klapka S-R z bramką NOR, ta również ma cztery stany. Są to

S=1, R=0-Q=0, Q’=1

Stan ten nazywany jest również stanem SET.

S=0, R=1-Q=1, Q’=0

Stan ten nazywany jest stanem RESET.

W obu stanach można zauważyć, że wyjścia są tylko komplementami siebie nawzajem i że wartość Q podąża za wartością komplementu S.

S=0, R=0-Q=1, & Q’ =1

Jeśli obie wartości S i R są przełączone na 0 to jest to stan nieprawidłowy, ponieważ wartości zarówno Q jak i Q’ są 1. Powinny one być komplementarne względem siebie. Normalnie należy unikać tego stanu.

S=1, R=1-Q & Q’= Remember

Jeśli obie wartości S i R są przełączone na 1, to układ pamięta wartość S i R w ich poprzednim stanie.

-

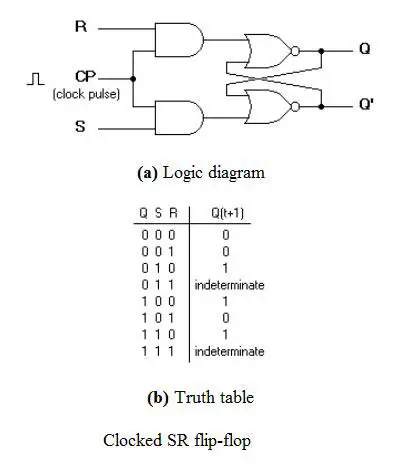

Clocked S-R Flip Flop

Jest on również nazywany Gated S-R flip flop.

Problemem w przypadku klapek S-R wykorzystujących bramki NOR i NAND jest stan nieważny. Problem ten można przezwyciężyć stosując bistabilną klapkę SR, która może zmieniać wyjścia, gdy spełnione są pewne stany nieważne, niezależnie od stanu wejść Set lub Reset. W tym celu zaprojektowano taktowaną klapkę S-R poprzez dodanie dwóch bramek AND do podstawowej klapki NOR Gate. Schemat układu i tabela prawdy są pokazane poniżej.

Puls zegarowy jest podawany na wejścia bramki AND. Gdy wartość impulsu zegarowego wynosi „0”, wyjścia obu bramek AND pozostają „0”. W momencie podania impulsu wartość CP zmienia się na '1′. To powoduje, że wartości S i R przechodzą przez klapkę NOR Gate. Ale kiedy wartości zarówno S jak i R zmieniają się na '1′, wartość HIGH CP powoduje, że obie te wartości na krótką chwilę zmieniają się na '0′. Jak tylko impuls zostanie usunięty, stan klapki staje się pośredni. Tak więc każdy z tych dwóch stanów może być wywołany, a zależy to od tego, czy wejście set lub reset klapki pozostaje '1′ dłużej niż przejście do '0′ na końcu impulsu. W ten sposób można wyeliminować stany nieprawidłowe.

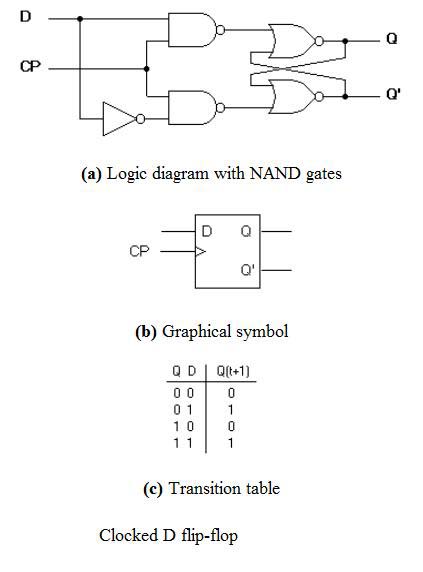

D Flip Flop

Schemat układu i tabela prawdy jest podana poniżej.

D flip flop jest właściwie lekką modyfikacją wyżej wyjaśnionego clocked SR flip-flop. Z rysunku widać, że wejście D jest podłączone do wejścia S, a dopełnienie wejścia D jest podłączone do wejścia R. Wejście D jest przekazywane do przerzutnika, gdy wartość CP wynosi '1′. Gdy CP jest HIGH, klapka przechodzi w stan SET. Jeśli jest '0′, klapka przechodzi w stan CLEAR.

Aby dowiedzieć się więcej o wyzwalaniu klapek kliknij na poniższy link.

TAKE A LOOK : TRIGGERING OF FLIP FLOPS

TAKE A LOOK : MASTER-SLAVE FLIP FLOP CIRCUIT

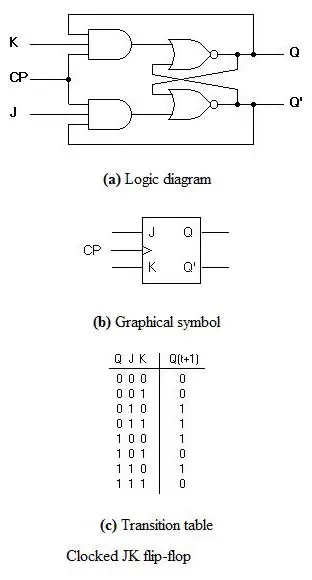

J-K Flip Flop

Schemat obwodu i tabela prawdy dla J-K flip flop są pokazane poniżej.

J-K flip flop może być również zdefiniowany jako modyfikacja S-R flip flop. Jedyna różnica polega na tym, że stan pośredni jest bardziej wyrafinowany i precyzyjny niż w przypadku klapki S-R.

Zachowanie wejść J i K jest takie samo jak wejść S i R klapki S-R. Litera J oznacza SET, a litera K oznacza CLEAR.

Gdy oba wejścia J i K mają stan HIGH, klapka przechodzi w stan dopełnienia. Czyli dla wartości Q = 1, przełącza się na Q=0, a dla wartości Q = 0, przełącza się na Q=1.

Obwód zawiera dwie 3-wejściowe bramki AND. Wyjście Q klapki jest zwracane jako sprzężenie zwrotne do wejścia AND wraz z innymi wejściami, takimi jak K i impuls zegarowy. Tak więc, jeśli wartość CP wynosi '1′, klapka otrzymuje sygnał CLEAR i to pod warunkiem, że wartość Q była wcześniejsza o 1. Podobnie wyjście Q’ z klapki jest podawane jako sprzężenie zwrotne na wejście AND wraz z innymi wejściami jak J i impuls zegarowy . Tak więc wyjście staje się SET, gdy wartość CP wynosi 1 tylko wtedy, gdy wartość Q’ była wcześniej 1.

Wyjście może się powtarzać w przejściach po ich dopełnieniu dla J=K=1 z powodu połączenia zwrotnego w klapce JK. Można tego uniknąć ustawiając czas trwania mniejszy niż opóźnienie propagacji przez klapkę. Ograniczenie szerokości impulsu można wyeliminować stosując konstrukcję master-slave lub wyzwalaną zboczem.

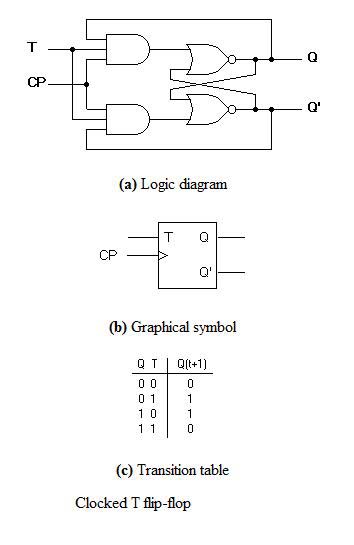

T Flip Flop

Jest to znacznie prostsza wersja klapki J-K. Oba wejścia J i K są połączone razem i dlatego nazywana jest również jedno-wejściową klapką J-K. Po podaniu impulsu zegarowego na klapkę, jej wyjście zaczyna się przełączać. Tutaj również ograniczenie szerokości impulsu może być wyeliminowane dzięki konstrukcji master-slave lub edge-triggered. Przyjrzyj się układowi i tabeli prawdy poniżej.

.